|

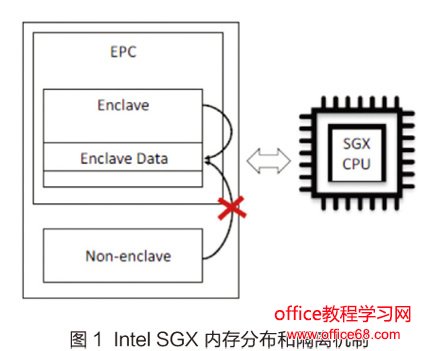

Intel SGX技术是一种新的基于硬件的可信计算技术。该技术通过CPU的安全扩展,对用户空间运行环境(enclave)提供机密性和完整性保护。即使是攻击者获得OS、hypervisor、BIOS和SMM等权限,也无法直接攻击enclave。因此,攻击者不得不通过侧信道的攻击方法来间接获取数据(比如隐私数据,加密密钥等)。得益于enclave的强安全假设和工作模型,攻击者有大量的侧信道攻击面可以选择,比如页表、Cache、DRAM等。这项工作是对侧信道攻击面进行一个全面的总结,并讨论一些可能的防御和检测方法。 当我们不能够完全相信某个计算平台(比如公有云和可能被攻破的操作系统)的时候,建立一个可信的运行环境(TEE)是非常重要的安全要求。近些年研究人员提出了很多TEE系统用于保护应用程序,使其能够抵御来自操作系统的攻击。 Enclave的运行环境有大量的资源和外面non-enclave公用,比如Cache、页表、DRAM和分支预测器等,这就给攻击者提供了丰富的侧信道攻击面。而且,不可信的操作系统还仍然负责管理系统的资源,比如页表、内存、中断、进程调度等,这就进一步方便攻击者减小侧信道攻击过程中的噪音,从而提高侧信道攻击的成功率。 本文主要调研和总结目前已有的侧信道攻击。根据攻击面的不同,将从页表、TLB、Cache、DRAM和分支预测器等几个面进行侧信道攻击的介绍。SGX的侧信道攻击十分难以防御。目前还没有一种防御策略可以防御以上所有攻击。本文最后对可能的侧信道防御攻击方法进行简要的总结,希望读者能够在某些方面受到启发。 SGX背景介绍 Intel SGX是一种基于硬件的TEE系统。该功能已经集成在Intel Sky-Lake系列。区别以往的TEE系统有着较大的可信计算基(TCB),SGX的可信计算基非常小,仅仅包含CPU和enclave本身。任何的特权软件,比如OS、hypervisor、BIOS、SMM等都不包含在可信计算基内。Enclave有SGX硬件专门预留的EPC(Enclave Page Cache)内存。EPC是PRM(processor reserved memory)的子集,并被系统软件按照4KB粒度进行分页管理。每一个EPC页面只能分配给一个enclave。CPU阻止任何nonenclave去访问PRM,任何non-enclave的访问都会导致一个失败的事务(abortedtransaction)。在目前SkyLake的处理器上面,失败的写操作被忽略,失败的读操作直接返回一个全1的值。 每个enclave的程序指定一段ELRANGE(Enclave Linear AddressRange)的虚拟空间供自身运行。页表负责把虚拟地址映射为EPC所在的物理地址。页表的工作原理和以往的页表一样,比如会进行权限的检测、会设置access bit和dirty bit等等。Enclave和non-enclave可以通过EENTER和EEXIT来主动切换工作模式。Enclave运行时可能会被中断或者异常打断,这个时候enclave会通过AEX(Asynchronous EnclaveExit)机制退出,切换到non-enclave工作模式。在模式切换过程中,运行状态会保存到SSA(StateSave Area)结构体里面,同时清除TLB以保证enclave的安全。 图1是Intel SGX内存分布和隔离机制。Enclave跑在EPC上面。Enclave的数据仅可以被enclave自己访问,任何外界代码的访问都会被拒绝。

SGX侧信道攻击 威胁模型 侧信道攻击主要目标是攻击enclave数据的机密性(confidentiality)。攻击者来自non-enclave部分,包括应用程序和系统软件。系统软件包括OS、hypervisor、SMM、BIOS等特权级软件。 侧信道攻击一般假设攻击者知道enclave初始化时的代码和数据,并且知道内存布局。内存布局包括虚拟地址,物理地址以及他们之间的映射关系。侧信道攻击还假设攻击者知道运行enclave平台的硬件配置、特性和性能,比如CPU、TLB、Cache、DRAM、页表、中断以及异常等各种系统底层机制。 侧信道的攻击面 enclave和non-enclave共享大量的系统资源,这就给侧信道攻击留下了非常大的攻击面。经过对现有资料的总结和系统结构的分析,我们把SGX 的攻击总结在图2中。如图2所示,enclave的运行过程中会用到:

1.CPU内部结构。比如pipeline,branch prediction Buffer(BPB)等,这些结构不能够直接访问,但是如果可以间接利用,仍然可能泄露enclave的控制流或数据流。 2.TLB。TLB有包括iTLB、dTLB和L2 TLB。如果HyperThreading打开,两个逻辑核共享一个物理核,这个时候会大大增加侧信道的可能。 3.Cache。Cache包括L1 instructionCache、L1 data Cache、L2Cache 和L3Cache(又叫LLC Cache)。 4.DRAM。DRAM包含channels、DIMMs、ranks、banks。每个banks又包含rows、columns和row buffer。 5.Pagetable(页表)。页表可以通过权限控制来触发缺页异常,也可以通过页表的状态位来表明CPU的某些操作。对于不同的攻击面,攻击者需要了解具体的细节和工作原理。其中比较重要的参考的文档就是Intel的手册。目前SGX已经部署在SkyLake的机器上面。因此我们需要对SkyLake的一些硬件和性能细节重点掌握。 侧信道攻击 侧信道攻击主要手段是通过攻击面获取数据,推导获得控制流和数据流信息,最终获取被enclave的代码和数据的信息,比如加密密钥、隐私数据等等。在此一一列举具体的工作,而是试图从攻击面的角度,全面的介绍侧信道攻击。本章节下面的内容,就从典型的攻击面,包括页表、TLB、Cache、DRAM以及CPU内部结构,描述目前已知的侧信道攻击。 1.基于页表的攻击 最早的SGX侧信道攻击就是基于页表的攻击。这类利用页表对enclave页面的访问控制权,设置enclave页面为不可访问。这个时候任何访问都会触发缺页异常,从而能够区分enclave访问了哪些页面。按照时间顺序把这些信息组合,就能够反推出enclave的某些状态和保护的数据。该类典型的攻击包括controlledchannelattack和pigeonholeattack。这类攻击的缺点就是精度只能达到页粒度,无法区分更细粒度的信息。但是在某些场景下,这类攻击已经能够获得大量有用信息。 后来,基于页表的攻击有了新的变种。这些侧信道攻击主要利用页表的状态位。一个页表项有很多位,有些是用来做访问控制,比如P,RW,US,XD,有些则标识状态,比如D(dirty bit)和A(accessbit)。如果A bit被设置,则表明该页表项指向的页面已经被访问;如果Dbit被设置,则表明该页表项指向的页面发生了写操作。通过监控观察这些状态位,攻击者就可以获取和controlled-channel/pigeonhole攻击类似的信息。 2.基于TLB的攻击 目前还没有完全基于TLB的攻击,但是已经出现TLB作为辅助手段的侧信道攻击。关于TLB的两点重要信息,我们需要了解,希望对提出新的基于TLB的侧信道攻击和防御有所帮助。 TLB的层次结构:目前SkyLake的机器,分为L1和L2两层。不同层次出现的TLB miss的时间代价不同。 TLB对代码和数据的区分:L1区分代码(iTLB)和数据(dTLB)。两者直接有Cache coherence的保证。L2不区分代码和数据。 3.基于Cache的攻击 传统侧信道有很多基于Cache的攻击在SGX的环境里面,这些侧信道技术仍然适用,而且可以做的更好。原因在于,在SGX环境里面攻击者可以控制整个系统的资源。因此,攻击者可以有针对性地调度资源,减小侧信道的噪音,增加侧信道的成功率。降低噪音的策略大体可以有以下几种。 Core Isolation(核隔离)。这个方法的主要目标就是让enclave独自占有一个核(不允许其他程序运行在该核上面)。Cache Isolation( 缓存隔离)。尽量使用L1或者L2级别的Cache进行侧信道攻击。L3的Cache被所有的核共用,会引入不必要的噪音。 Uninterupted Execution(不间断运行)。也就是不触发或尽量少触发AEX,因为AEX和后续的ISR(Interrupt SeviceRountine)都会使用Cache,从而引入不必要噪音。少触发AEX就是要使用中断绑定(Interrupt Affinity)和将时钟频率。不触发AEX基本上就是让系统软件(比如OS)屏蔽所有中断。 除了降低噪音,攻击者还可以提高攻击的精度,大体策略有:一是高精度时钟。可以采用APIC提供的高精度时钟和硬件TSC;二是放大时间差异。比如攻击者可以配置侧信道攻击代码所在的CPU以最高频率运行,而对enclave所在的CPU进行降频处理。 基于Cache的侧信道攻击可以进行细粒度的监控。最小粒度可以做到一个Cache line,即64个字节。由于粒度更小,基于Cache 的侧信道可以比基于页表的侧信道(以及后面介绍的基于DRAM的侧信道)获得更多的信息。 4.基于DRAM的攻击 RAM一般由channel、DIMM、rank、bank等部分构成。每个bank又有columns和rows组成。每个bank里面还有一个row buffer用来缓存最近访问过的一个row。在访问DRAM的时候,如果访问地址已经被缓存在rowbuffer当中(情况A),就直接从buffer里面读取,否则需要把访问地址对应的整个row都加载到row buffer当中(情况B)。当然,如果row buffer之前缓存了其他row的内容,还需要先换出row buffer的内容再加载新的row(情况C)。A、B、C对应的三种情况,访问速度依次递减(情况A最快,情况C最慢)。这样,通过时间上的差异,攻击者就可以了解当前访问的内存地址是否在row buffer里面,以及是否被换出。 基于DRAM的侧信道攻击有一些不足:第一,enclave使用的内存通常都在缓存里面,只有少部分需要从DRAM里面去取;第二,DRAM的精度不够。例如,一个页面(4KB)通常分布在4个DRAMrow上面。这样,基于DRAM的侧信道攻击的精度就是1KB。仅仅比基于页表的侧信道攻击好一些,远远不及基于Cache的侧信道攻击的精度;第三,DRAM里面存在很难避免的噪音干扰,因为一个DRAMrow被很多页面使用,同时同一个bank不同row的数据读取也会对时间测量造成干扰,使得误报时常发生。 5.基于CPU内部结构的攻击 CPU内部有大量的结构是在enclave和non-enclave之间共用的,这就给侧信道攻击提供了大量的攻击面素材。 目前对以CPU内部结构为攻击面的工作才刚刚开始,仅仅有一个工作发表。相信通过进一步研究,还会有其他的攻击面被陆续发掘。 从设计上来讲,SGX可以避免这类侧信道攻击。具体来讲,在enclave到nonenclave的切换过程中,CPU清除这些共用的内部结构体。这样,non-enclave就不会得到任何残留的记录。但在具体实现的时候,还要注意一些细节,比如清除的时间也必须是稳定不变的。如果enclave运行的差异会导致清除操作的时间差异,攻击者很可能据此推导出enclave的某些运行状态。 6.混合侧信道攻击 混合侧信道攻击是同时采集多个侧信道攻击面的信息,或通过多个攻击面共同作用放大差异增加准确度。比较典型的做法包括:一是TLB和页表混合攻击。比如TLB miss的时会加载页表,这个时候CPU会设置页表的Access bi;二是Cache和DRAM混合攻击。基于DRAM的攻击只能精确到row(一个row通常8KB)的粒度。 除了结合两个攻击面的侧信道攻击,还可以采用多个攻击面相结合的侧信道攻击。这类混合攻击我还没有在SGX的环境下面看到相关工作。 7.未来可能的侧信道攻击 未来新的侧信道攻击可能来自两个方面。第一就是发掘新的混合侧信道攻击。前面列出的经典的混合侧信道攻击,他们往往使用两种攻击面信息。因此,我们可以考虑多个攻击面结合的侧信道攻击。以往的混合侧信道攻击往往专注于内存管理和地址转换等方面,新的侧信道攻击可以结合其他方面的信息,进行一些新的尝试。 enclave所有和non-enclave共享的资源都可能成为潜在的侧信道攻击面。因此,发掘新的侧信道攻击的第二个途径就是发现新的共享资源,比如未被发掘的CPU内部共享结构。这些新的的共享资源可能来自一些新的硬件特性,比如Intel PT、Intel TSX、Intel MPX、IntelCAT等。 可能的防御方法 目前已经有很多文章给出了防御SGX侧信道的方案,有些只是大体的思路,有些则已经有成型的设计和实现。我们在这里主要介绍防御的思路和方法,不涉及设计和实现的细节。首先,我们把这些方法涉及的层次,分为源码级别,系统级别和硬件级别。 1.源码层次的解决方案 这类方法的主要思想就是通过修改源码,编写出能够防御侧信道的代码实现,其核心思想就是隐藏控制流和数据流。这类方法的探索已经在一些密码算法中有所涉及。 2.系统层次的解决方案 系统层次的解决方案主要是利用一些系统特性来防御或检测SGX侧信道。这里有几个思路可以参考:随机化技术(Randomization)、检测可疑异常和中断、检测时间异常、Cache隔离。 3.硬件层次的解决方案 硬件层次的解决方案还处于探索阶段。加上侧信道防御,将会显著增加硬件复杂度,影响功耗和性能。这也可能是Intel在最初推出SGX的时候没有加入侧信道防御的一个原因。硬件解决方案可能有硬件分割和硬件隔离两种。 本文总结了SGX所面临的侧信道攻击,并展望了潜在的攻击和防御方法。SGX的侧信道攻击十分难以防御。究其原因是SGX的安全假设和应用模型允许enclave和不可信的non-enclave共享大量的资源。这些就给攻击者以很大的攻击面去区分时间上的差异和资源使用的不同,从而泄露enclave的控制流和数据流。而且攻击者拥有管理系统资源的能力,从而能够最大程度上减小噪音干扰,增加侧信道攻击的成功率。总之,SGX侧信道攻击是一个实用的攻击,我们在实际部署应用SGX的时候,必须考虑潜在的侧信道攻击。(责编:杨洁) (作者单位为百度美国研究院安全实验室) (本文刊载于《中国教育网络》2018年4月刊) |